## Compito di Architettura dei Calcolatori

## Compito di Macchine per l'elaborazione dell'Informazione 01/06/2016

| Nome | Cognome |

|------|---------|

|      |         |

|      | ·       |

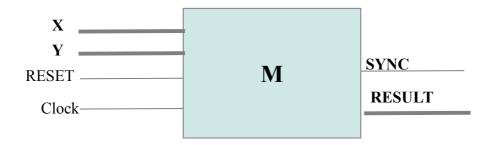

Progettare e sviluppare in VHDL una macchina che accetta in ingresso:

- un **clock** di periodo 5 us,

- un segnale di reset,

- due segnali X e Y da 1 bit

- un segnale SEL da 2 bit

La macchina presenta in uscita:

- un segnale SYNC da 1 bit

- un segnale **RESULT** da **9** bit

## La macchina riceve continuamente bit sui segnali X e Y.

A partire dal reset la macchina azzera i registri interni e si pone in uno stato di ricerca dello stesso carattere di sincronizzazione "101010101" da 9 bit su X e Y.

Al riconoscimento di tale carattere la macchina alza il segnale **SYNC** e comincia a operare ogni 9 colpi di clock sui bit ricevuti in sequenza.

Dopo la sincronizzazione, l'ultimo bit di ogni 9 è il bit di parità. Se il controllo di parità (**pari**) è errato la macchina abassa **SYNC** e si pone nuovamente in uno stato di ricerca.

In funzione delle linee **SEL** la macchina usa i primi 8 bit della sequenza di 9 per fornire in uscita (**RESULT**) la *somma* degli ultimi due byte ricevuti, la *differenza*, *XOR* o *AND*.

Il bit più significativo di RESULT contiene riporto o prestito, o viene lasciato a 0 nel caso di operazioni logiche.